初めてでも使えるVerilog HDL文法ガイド ―― 記述スタイル編 小林 優 tag 半導体 ディジタル・デザイン 技術解説 09年7月10日 Tweet シフトレジスタもどき verilog シフトさせまくって64bit分溜まったら吐き出す 吐き出すとき、Enableがたつ 使えるかどうかは、要確認 module Shift64 #( parameter DATA_WIDTH = 64, parameter LOG_WIDTH = 6 )( input InData, output reg (DATA_WIDTH1)0 OutData, input CLK50M, outp説明 Shift Arithmetic ブロックでは、入力信号のビットまたは 2 進小数点あるいはその両方をシフトできます。 たとえば、データ型 sfix(8) の入力で 2 進小数点を右または左に 2 桁シフトした結果は以下の 10 進数の値になります。

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

Verilog シフトレジスタ 配列

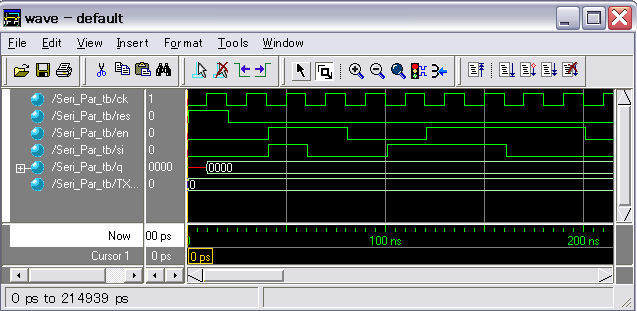

Verilog シフトレジスタ 配列-SystemVerilogでは多次元配列を扱えるようになった。 いまさら例を出すまでもないが、8bit長のレジスタを宣言するには、以下のようにしていた。 reg 70 a; 電気回路 HDL ISim による Verilog テストベンチ (木) 1125 (926d) 更新 印刷しないセクションを選択 公開メモ 概要 クロック 逐次処理

Verilog Hdl Tutorial 11

VerilogHDLは1次元配列しかサポートしませんが、SystemVerilogは、多次元配列をサポートします。 配列へのアクセスが容易になり記述量が減ります。 logic mem 255 0 ; verilogで二次元配列なんて書くことないと思ってたんだけどレジスタとか書くときに二次元配列すると楽なんですね。 `define BIT 32 `define ADDR 64 reg 0`BIT1 register 0`ADDR1;233 レジスタ配列 レジスタ型の信号は配列を作ることができる(ネット型はできない)。 reg 310 mem0255;

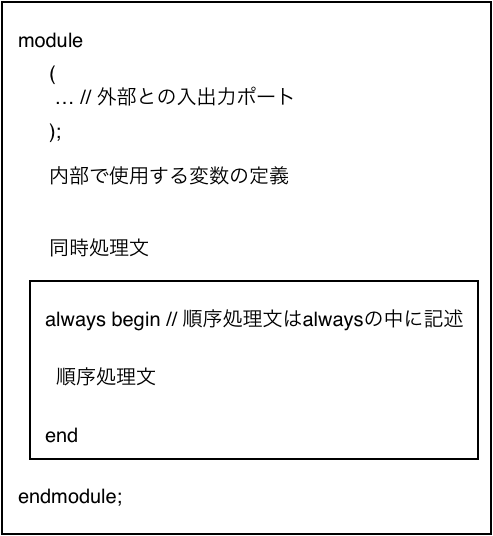

Verilog‐HDL 簡易文法書 reg レジスタ宣言: 値を保持する変数に対して宣言する。 wire ワイヤ宣言: 配線として使用する変数に対して宣言する。 (assign 文によって常時右辺の結果を出力する) ・ カウンタ,シフト・レジスタ フリップフロップの応用として,カウンタとシフト・レジスタの例を示します. リスト6(a) はロード優先のイネーブル付きカウンタです.ロード信号LDが'1'ならパラレル・ロードし,イネーブル信号ENが'1'ならカウントVerilog ISEの使い方 (レグ)はレジスタをモデル化した変数です。 Regやwireなどの変数は配列にすることができます。配列を宣言するためには、以下のように記述します。

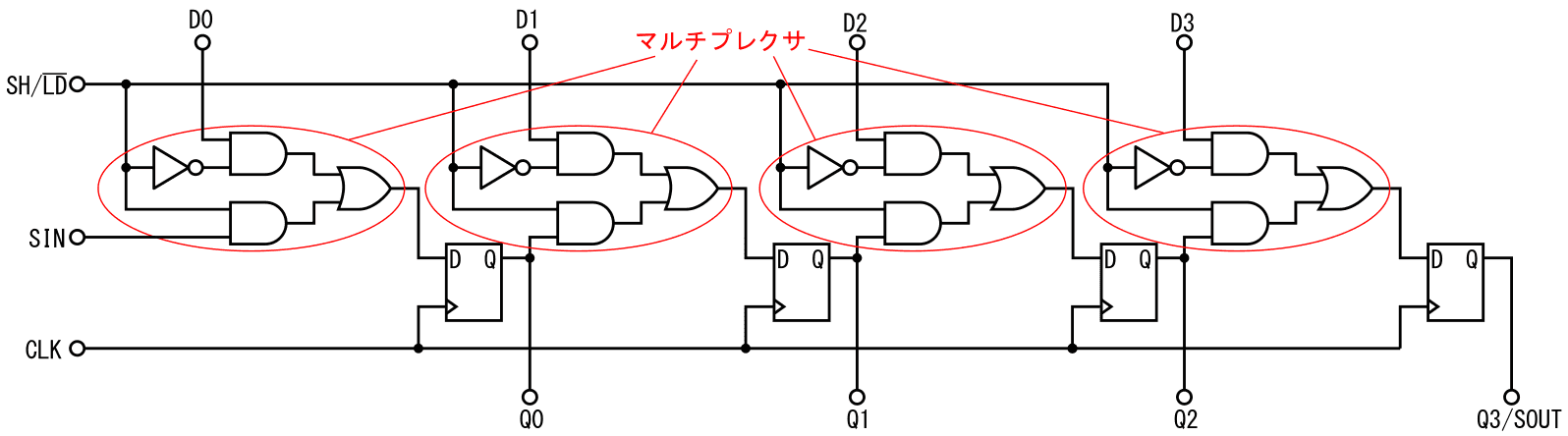

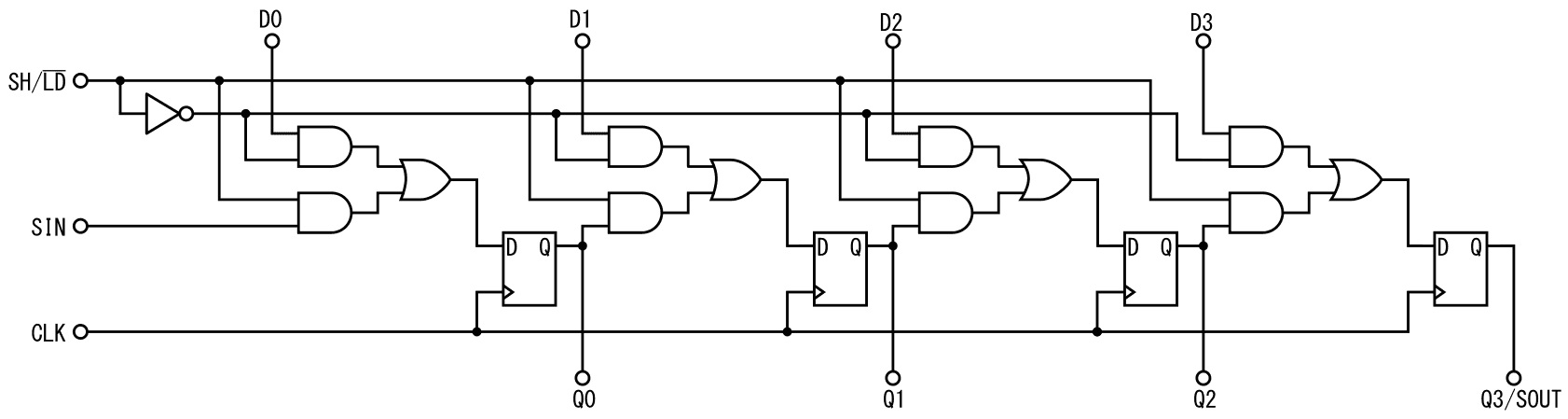

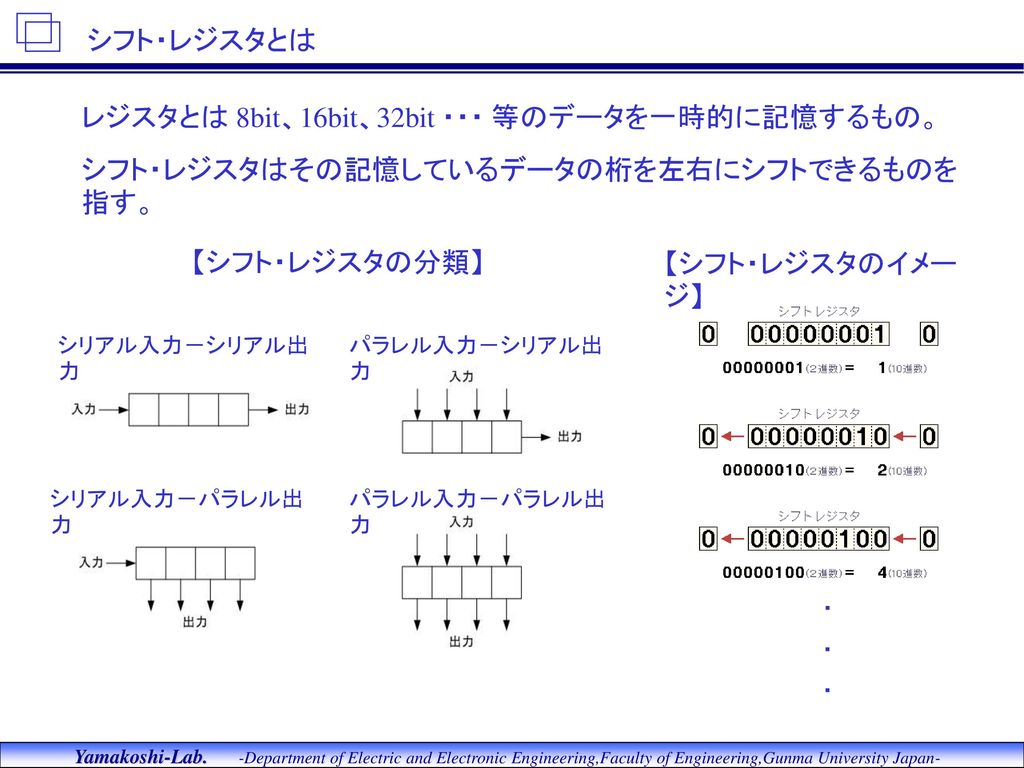

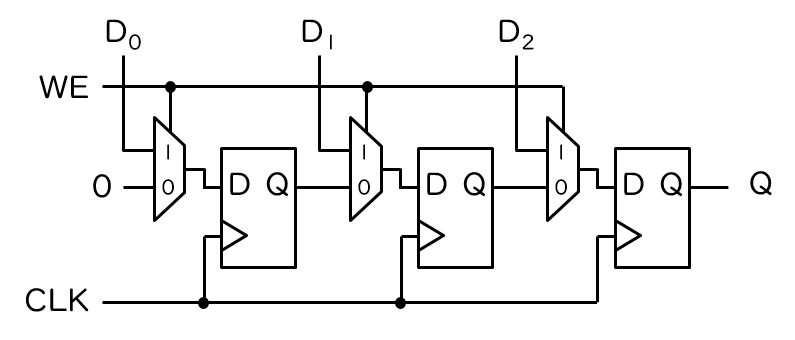

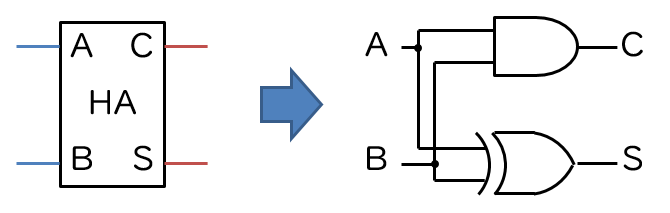

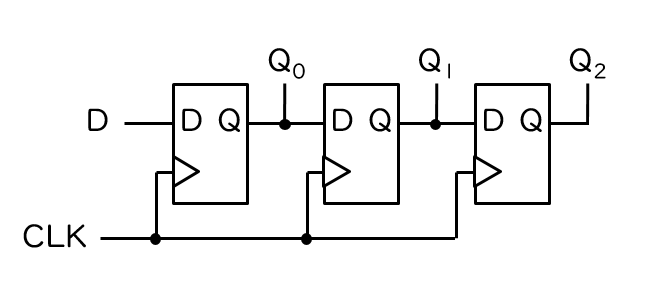

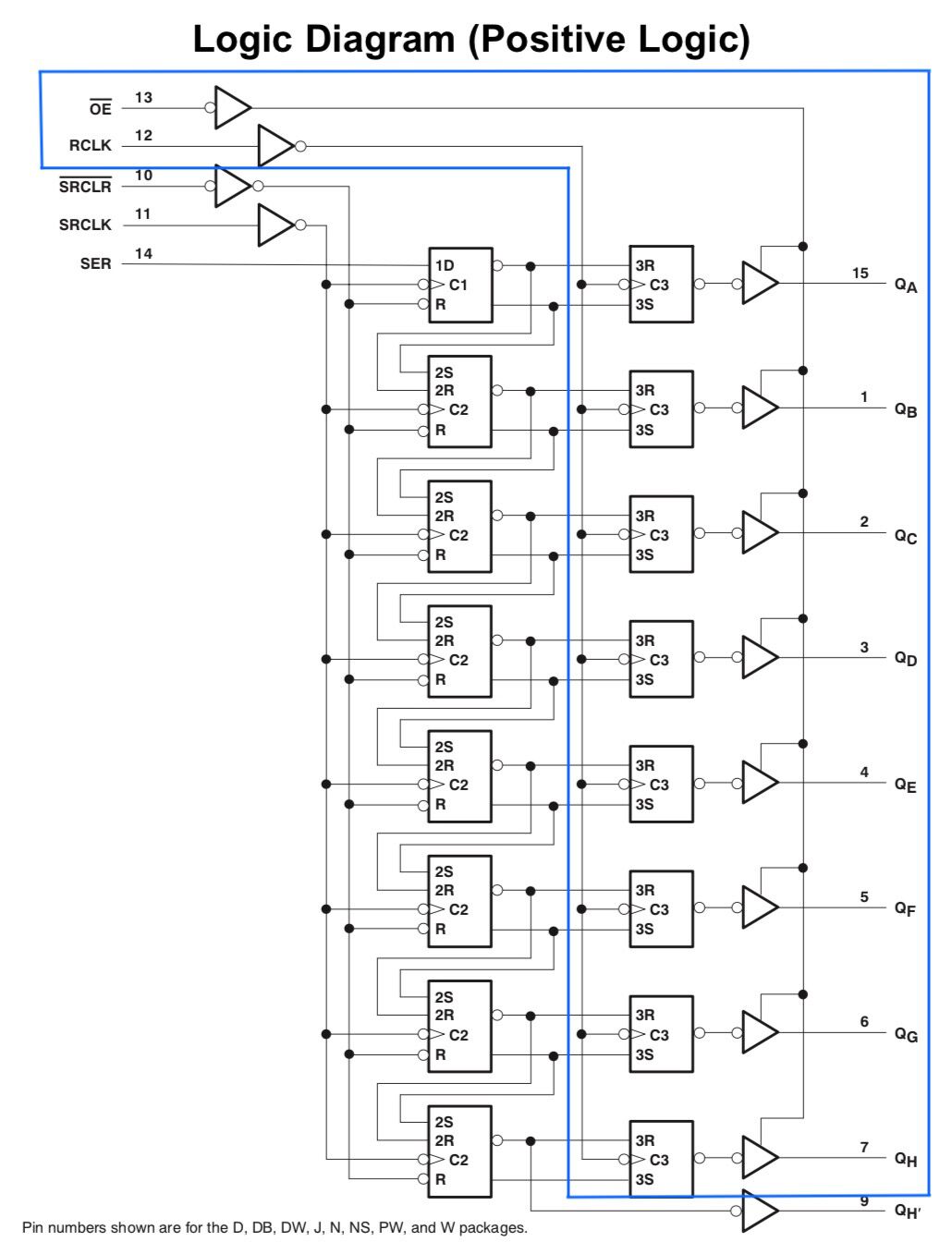

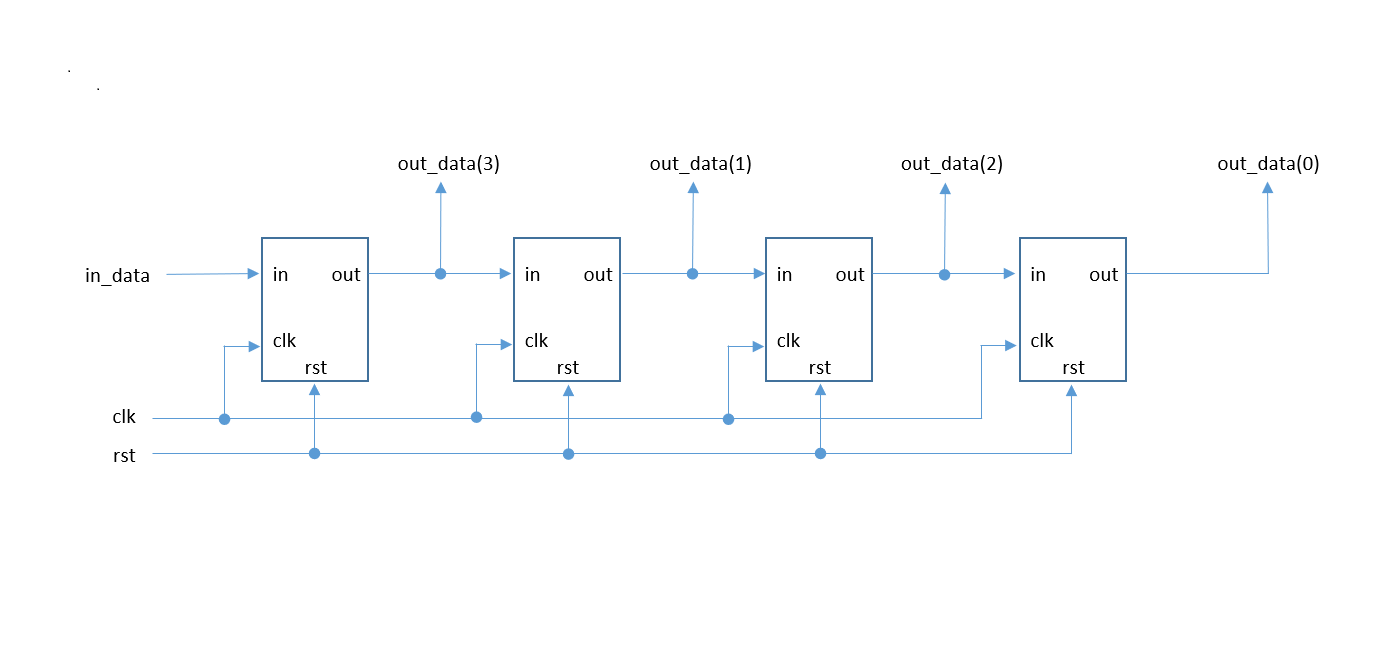

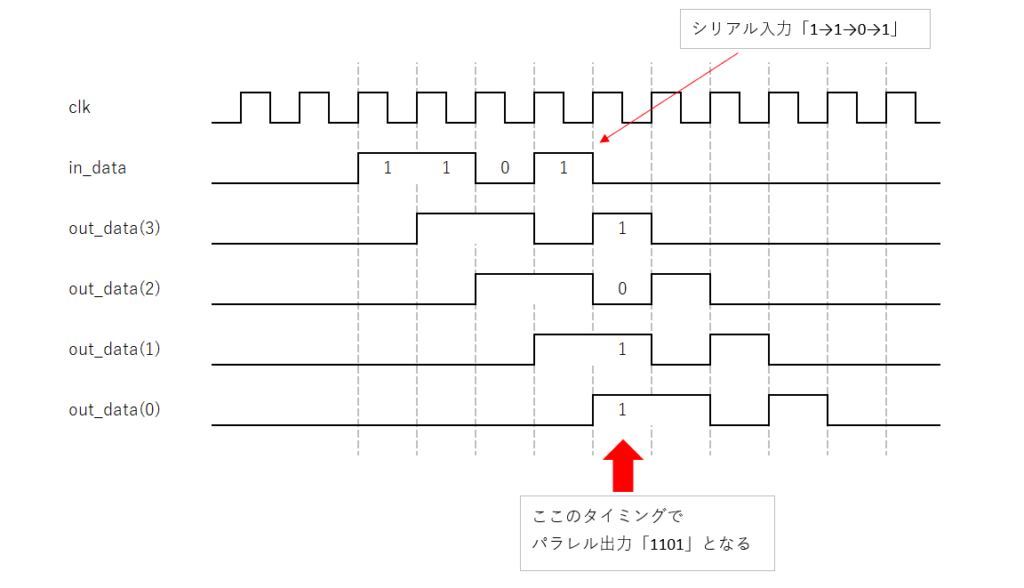

シフト >> 右シフト ツー Verilog HDLでは、整数、レジスタ(reg)、ベクトル(regまたはnetデータ型、いくつかのビット長)、および時間の配列が可能です。 配列の基本的な宣言を例とともに以下に示します。 Verilogでは、実変数の配列は許可されていVerilog VHDL 回路設計 シフトレジスタはDFFを連ねた回路ですが、いろいろな回路の基本となる事が多く、必ずマスターしておかなくてはならない回路構成です。 単純なシフトレジスタは入力の信号をクロック分遅延させる。という回路になります。Verilog VHDL 回路設計 シフトレジスタはDFFを連ねた回路ですが、いろいろな回路の基本となる事が多く、必ずマスターしておかなくてはならない回路構成です。 単純なシフトレジスタは入力の信号をクロック分遅延させる。という回路になります。

問題11 パラメタライズによる回路の記述 完全マスター 電子回路ドリル Iii 11 Monoist

遅延可変シフトレジスタ Vhdl よくわからないfpgaのこととか

ホワイト ペーパ デザイン パフォーマンス向上のための HDL コーディング法 WP231 (11) 06 年 1 月 6 日 wwwxilinxcojp 3 R け、シフト レジスタのリセットを使用しない。 乗算器と RAM 最新のザイリンクス FPGA アーキテクチャでは、すべてに専用の演算リソースがあ ります。 Verilogのデータ型として主に用いるのはwire (ネット型)とreg (レジスタ型)です。 wireは配線に対応し組み合わせ回路の記述に使えますが、regは記述の仕方によって組み合わせ回路になったり順序回路であるFFやラッチになったりします。 文法的には wire assign合成/シミュレーションデザインガイド UG626(v141)12年4月24日 該当するソフトウェア バージョン ISE Design Suite 141 ~ 143

新適当マイコン電子工作研究所 So Netブログ

Fpgaの信号処理論理 シフトと定数乗算

目的 多ビット信号の配列(二次元配列)を使用する。 宣言 レジスタ(メモリ) reg 70 r_data0127 // 8bit幅 128 個のレジスタ宣言 信号(Wire) wire 70 w_data0127 // 8bit幅 128 組の ワイヤ宣言 Verilog では ポートに二次元配列は使用できない。 配列の中の任意の8bitを取り出すのに、 hogefugafuga 8と書きましたが、エラーになってしまいました。配列の添え字には、変数は記述できないのでしょうか?とすると、他にどの様な書き方があるのでしょうか?教えてください。よろIEEE 規格改訂01 (本稿は一部Verilog01 前提) 文法はだいたいC 言語と同じ 構文、演算子、型のユルさなど ブロックが{ } じゃなくてbegin end なぐらいの違い 抽象度は回路図より少し上ぐらいの気持ちで レジスタ転送レベル レジスタ間の論理を記述

Verilogチュートリアル 3つ以上の重要なverilog演算子

15 号 プログラミング言語による論理回路記述から論理回路を生成するための装置及び方法 Astamuse

シフトレジスタ 1 1 0 0 (100) ③②① 論理回路Ⅱ 摂大・鹿間 0 0 jkffによるデータのシフト動作 ck (k)後 入力; 出力; ck (k1)立ち下り 出力; ffaのデータがffbにシフトした nビットシフトレジスタ:jkffをn段接続して構成できる 0 ck(k) q j q k >ck clr qa q j q k >ck clr qb VHDL/VerilogHDL差分 VHDLとVerilogHDLの記述方法についてメモ VHDLとVerilogHDLではほとんど記号的な記述方法に差があるのみで, ほとんどが機械的に可換である 以下では機械的には置き換えられない記述方法についてメモしておく ほとんどは書き方の問題で実装回路記述⾔語VerilogHDL 実験第⼀J2課題 1 佐藤証⻄9613 akashisatoh@uecacjp

2

Opencores By Verilog Source With Vhdl Translation

8bit長のレジスタの、4ワード分の配列を宣言するには以下の通り。 reg 70 a03;14年12月1日 修正: 10年8月3日 公開 内田智久 Esys, IPNS, KEK 回路設計未経験者向けに必要最低限のVerilogHDL文法を解説した入門書です。 専門家向けに書かれた市販書籍は情報が多すぎるため、回路設計初心者からみると最低限何をどのように使えば良いのか分かりません。 Verilog ではこれは言語仕様なので、警告も出ないのですよね。 計算のビット幅を決める「式中に現れる数値」にはビットシフト演算子の右辺は含まれないためです。 このように、全体のビット幅を決めるときに意味をなさない「数」としては、 3項演算子

シフトレジスタ の解説 しなぷすのハード製作記

情報画像学実験ii 実験1 論理回路

XSTユーザーガイ ド(Virtex6および Spartan6デバイス用) UG687(v114)09年12月2日私はトランスミッタとレシーバの両方のofdmシステムをプログラミングしています。ビットが行く最初の関数は、基本的にlfsrであるスクランブラです。私の多項式はx^7 x^4 1です。簡単には、レジスタの7番目と4番目のビットをxorし、シフトレジスタの新しい最初のビットにしますその値を入力Verilog HDL では、よく、メモリを 70 mem 0 1023 という風に表現しましたが、これは、1次元のパックド配列を1024個持った1次元のアンパック配列と見ることもできます。

2

2

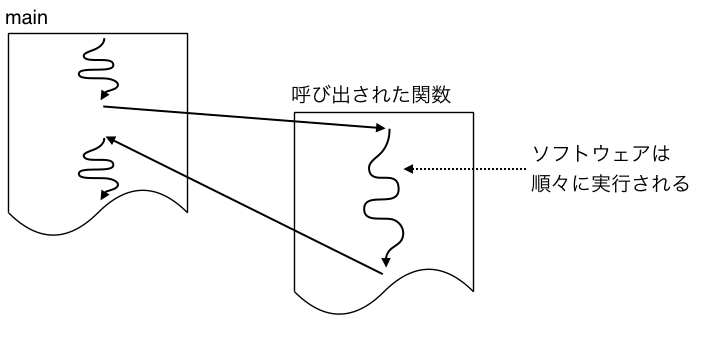

代入文の意味 「代入文」 変数=式; 「式」:単独の定数や変数,配列要素,及び それらを演算記号で結合したもの。 記号「=」は,右辺の式の「値」を左辺の変数に「格納」するという作用をもつ。例 単純なシフトレジスタの記述例2 この例は配列のスライスを使った例で、最も少ない式数で記述できるので スマートです。特にビット数の多いシフトレジスタになった時にも行数は 変わらず宣言の部分だけ修正すれば使えます。Verilog ISEの使い方 指定したビット数に応じて左または右方向にビットをシフトさせます。空いたビットには0が補完されます。

Vivado ユーザー ガイド

初めてでも使えるverilog Hdl文法ガイド 記述スタイル編 Tech Village テックビレッジ Cq出版株式会社

シフトレジスタ の解説 しなぷすのハード製作記

改訂 入門verilog Hdl記述

遅延可変シフトレジスタ Vhdl よくわからないfpgaのこととか

遅延可変シフトレジスタ Vhdl よくわからないfpgaのこととか

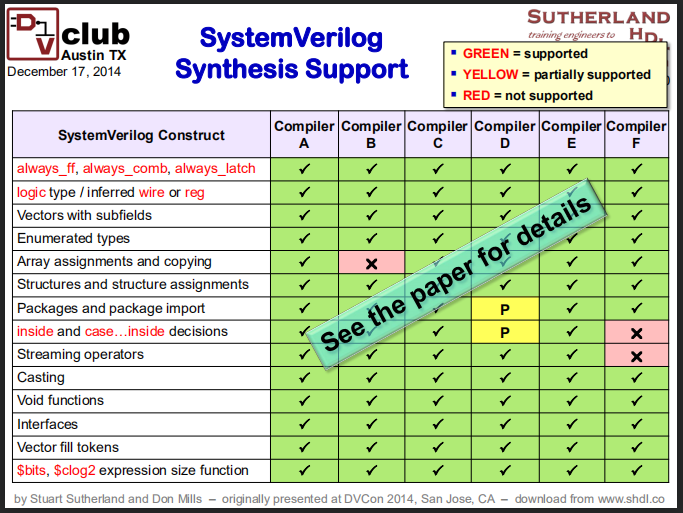

デザイン向け 論理合成可能 Systemverilog記述 Qiita

デザイン向け 論理合成可能 Systemverilog記述 Qiita

2

5 3 各種カウンタ 平木 Ppt Download

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

19 7745号 低減された配線複雑度を有するシフトレジスタ Astamuse

情報画像学実験ii 実験1 論理回路

Verilogでの配列 電子回路学習は続く

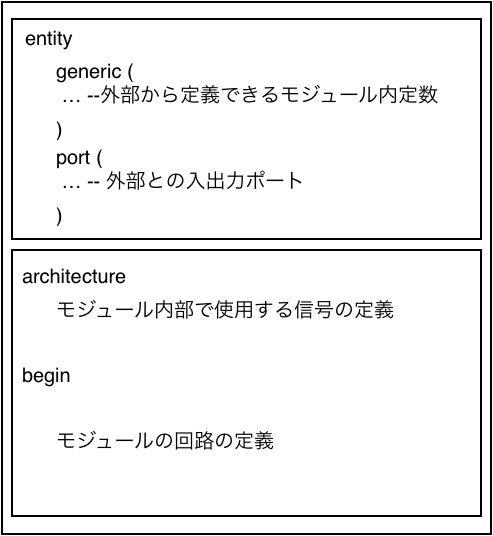

Vhdl 順序回路の記述法

Verilog Hdl Tutorial 11

遅延可変シフトレジスタ Vhdl よくわからないfpgaのこととか

Ppt 11 4 25 ディジタル情報回路 講義資料 Powerpoint Presentation Id

Verilogとは コンピュータの人気 最新記事を集めました はてな

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

情報画像学実験ii 実験1 論理回路

19 7745号 低減された配線複雑度を有するシフトレジスタ Astamuse

2

2

Verilogでの配列 電子回路学習は続く

2

多bit入力シフトレジスタの記述 小さな工作室

08 1427号 シフトレジスタ回路 シフトクロック発生回路及び画像処理装置 Astamuse

2

Labviewのループ反復間でデータを受け渡す National Instruments

2

Labview Mydaq 23 シフトレジスタと配列連結追加関数とを使う

Vhdl

遅延可変シフトレジスタ Vhdl よくわからないfpgaのこととか

デザイン向け 論理合成可能 Systemverilog記述 Qiita

遅延可変シフトレジスタ Vhdl よくわからないfpgaのこととか

Vhdl 順序回路の記述法

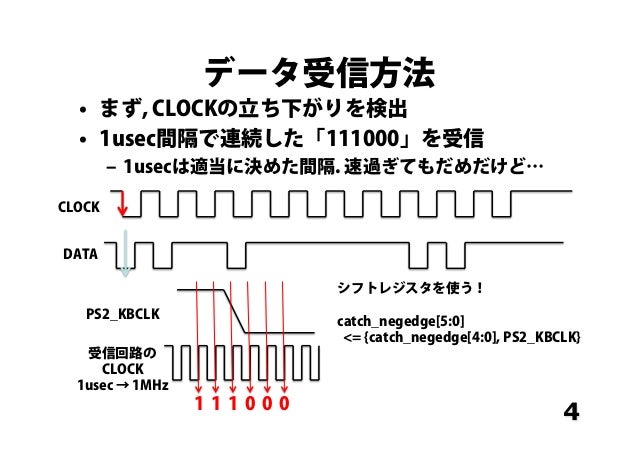

シリアル通信で Hello Fpga 1 Acri Blog

Verilogとは コンピュータの人気 最新記事を集めました はてな

Verilog Hdl Tutorial 11

覚え書き Verilog 擬似乱数生成

Labview Mydaq 23 シフトレジスタと配列連結追加関数とを使う

覚え書き Verilog 多ビット信号の配列 二次元配列

シフトレジスタ 電子回路学習は続く

Verilogでの配列 電子回路学習は続く

An 307 Xilinx ユーザー向けのアルテラのデザイン フロー Manualzz

2

シフトレジスタ 電子回路学習は続く

Systemverilog文法メモ Kivantium活動日記

デザイン向け 論理合成可能 Systemverilog記述 Qiita

Labviewのループ反復間でデータを受け渡す National Instruments

System Verilogにおける基本的なrtl記述と検証 エレプログ

2

Verilogでの変数 Reg の初期値設定 ハブ君の寝言

入門verilog Fpgaの部屋

Vhdl Veilog 入門 Learning Fpga

シリアル通信で Hello Fpga 1 Acri Blog

すzのavr研究 Machxo2

初めてでも使えるverilog Hdl文法ガイド 記述スタイル編 Tech Village テックビレッジ Cq出版株式会社

初めてでも使えるverilog Hdl文法ガイド 記述スタイル編 Tech Village テックビレッジ Cq出版株式会社

シリアル通信で Hello Fpga 1 Acri Blog

Vhdl Veilog 入門 Learning Fpga

Arduinoでシフトレジスタ Sn74hc595 を使用して8個のledをチカチカさせる Stupiddog S Blog

2

19 7745号 低減された配線複雑度を有するシフトレジスタ Astamuse

情報画像学実験ii 実験1 論理回路

シフトレジスタの回路図と記述法 Verilog Vhdl 組み込みエンジニアのメモ帳

情報画像学実験ii 実験1 論理回路

シフトレジスタのvhdl記述についてです 4ビット左シフトレジスタの場合 Yahoo 知恵袋

Vhdl

プログラムたった64行 Fpgaで創るオレオレ32bitcpu Tf32cpu R1 90mhz X 2コア動作 On Max10 Fpga Verilog Maker Kosen 福野泰介の一日一創 Create Every Day By Taisuke Fukuno

ハードウェア記述言語 その1

シフトレジスタ 電子回路学習は続く

Vhdl

2

初めての System Verilog Hassy S Tech Blog

ハードウェア記述言語 その1

Intended For Traditional Standard Cell Asic Designers Considering Fpga Or Hardcopy Asic Implementation Of Their Designs Either For Prototyping Or For Production Manualzz

Vhdl Veilog 入門 Learning Fpga

2

シリアル通信で Hello Fpga 1 Acri Blog

Verilogとは コンピュータの人気 最新記事を集めました はてな

シフトレジスタの回路図と記述法 Verilog Vhdl 組み込みエンジニアのメモ帳

遅延可変シフトレジスタ Verilog よくわからないfpgaのこととか

Vhdl Veilog 入門 Learning Fpga

6 代入文 代入文は 次の3種類があります 手続き代入文 Always Initialで使われる代入文 ブロッキング 代入文 Blocking Assignment 以下baと略 ノンブロッキング代入文 Nonblocking Assignment 以下nbaと略継続的代入文 Continous

08 1427号 シフトレジスタ回路 シフトクロック発生回路及び画像処理装置 Astamuse

Verilogチュートリアル 3つ以上の重要なverilog演算子

0 件のコメント:

コメントを投稿